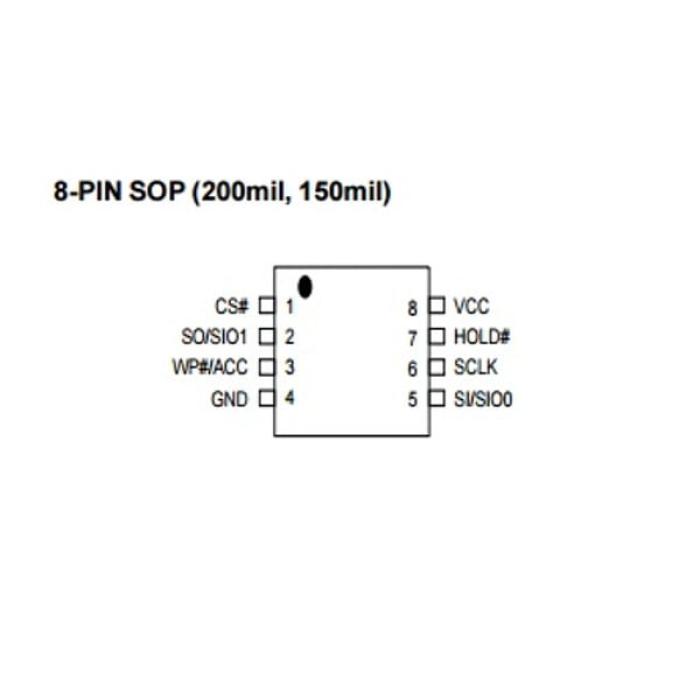

The MX25L3205D are 33,554,432 bit serial Flash memory, which is configured as 4,194,304 x 8 internally. When it is in two I/O read mode, the structure becomes 16,772,216 bits x 2 (please refer to the "Two I/O Read mode" section). The MX25L1605D/3205D/6405D feature a serial peripheral interface and software protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). Serial access to the device is enabled by CS# input. When it is in two I/O read mode, the SI pin and SO pin become SIO0 pin and SIO1 pin for address/dummy bits input and data output.The MX25L1605D/3205D/6405D provides sequential read operation on whole chip.After program/erase command is issued, auto program/ erase algorithms which program/ erase and verify the specified page or sector/block locations will be executed. Program command is executed on byte basis, or page (256 bytes) basis, or word basis for Continuously program mode, and erase command is executes on sector (4K-byte), or block (64K-byte), or whole chip basis.To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.Advanced security features enhance the protection and security functions, please see security features section for more details.When the device is not in operation and CS# is high, it is put in standby mode and draws less than 20uA DC current. The MX25L1605D/3205D/6405D utilizes MXIC's proprietary memory cell, which reliably stores memory contents even after typical 100,000 program and erase cycles.